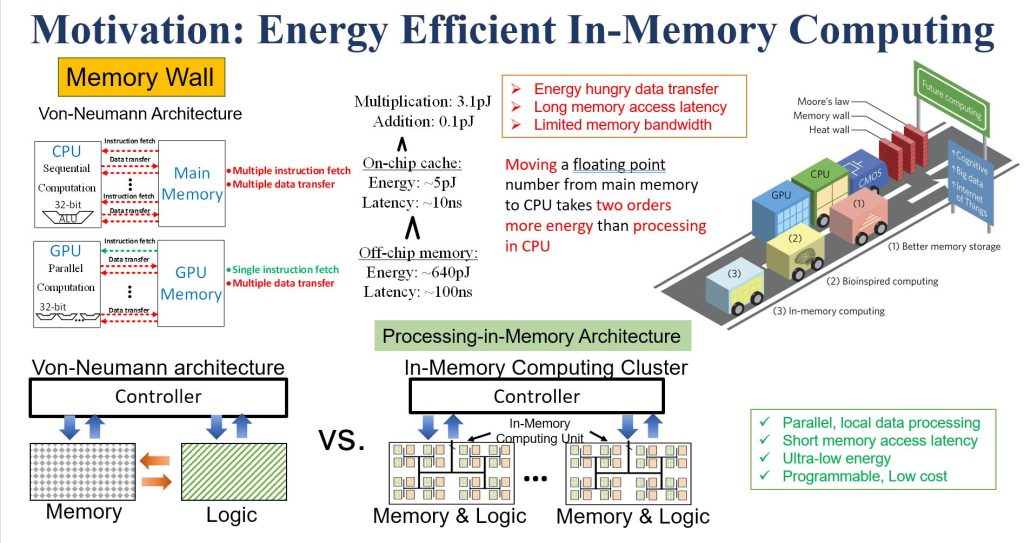

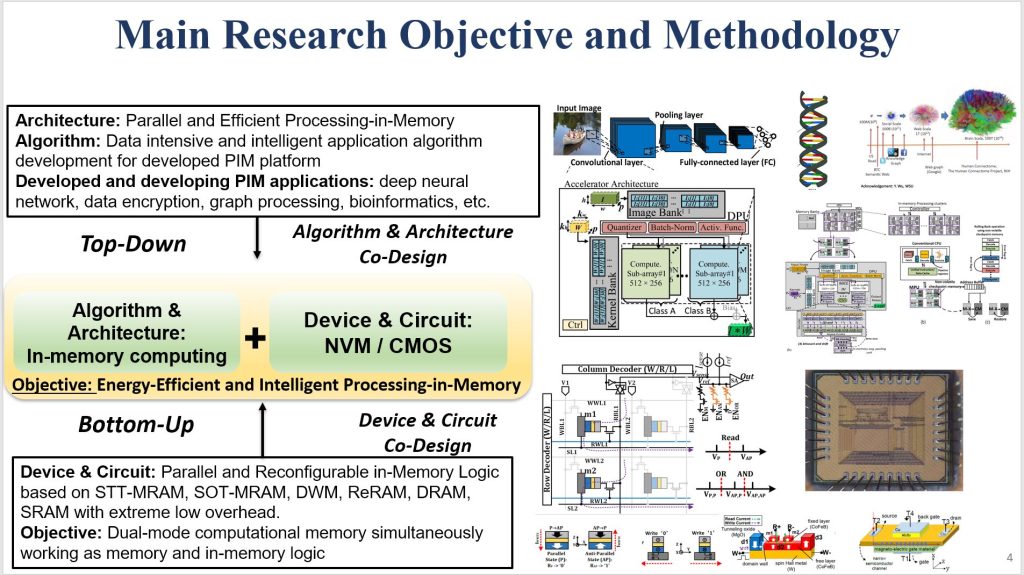

In-Memory Computing

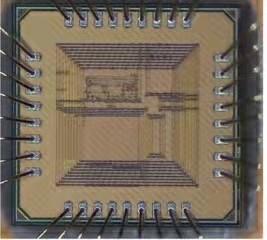

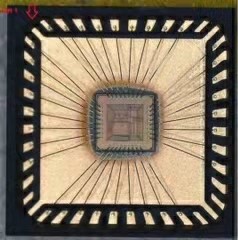

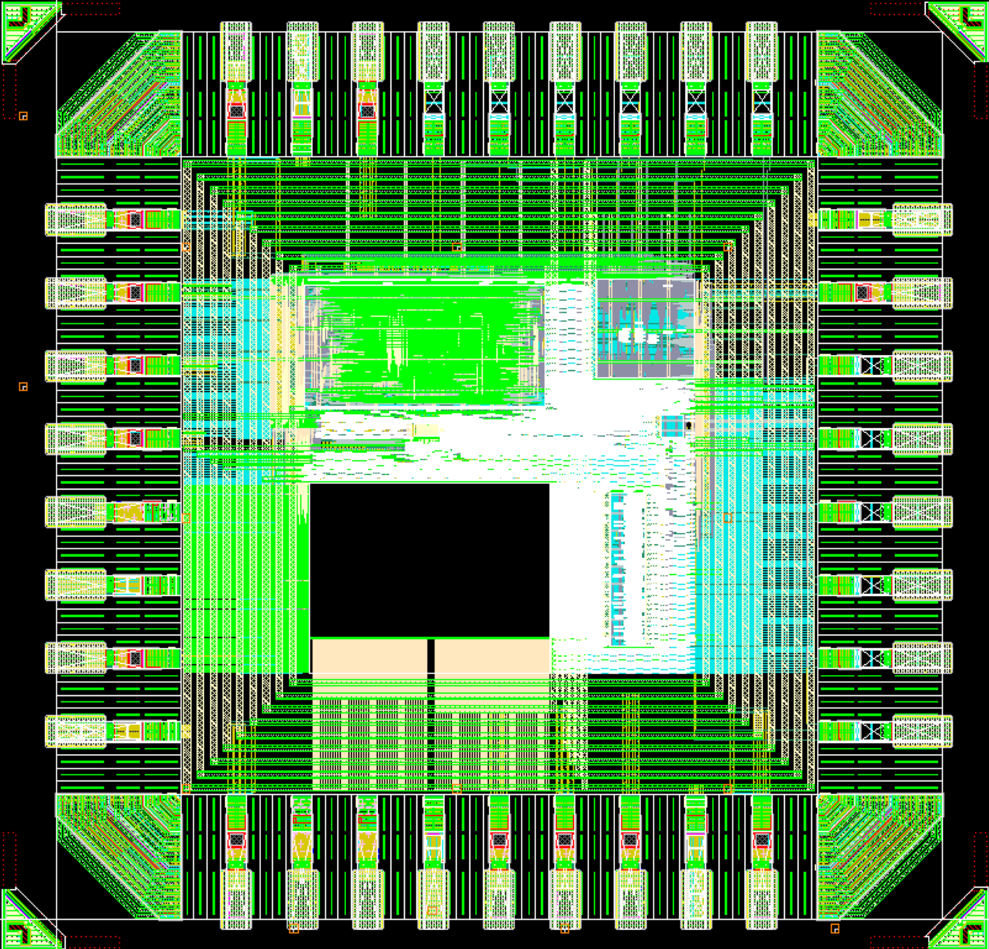

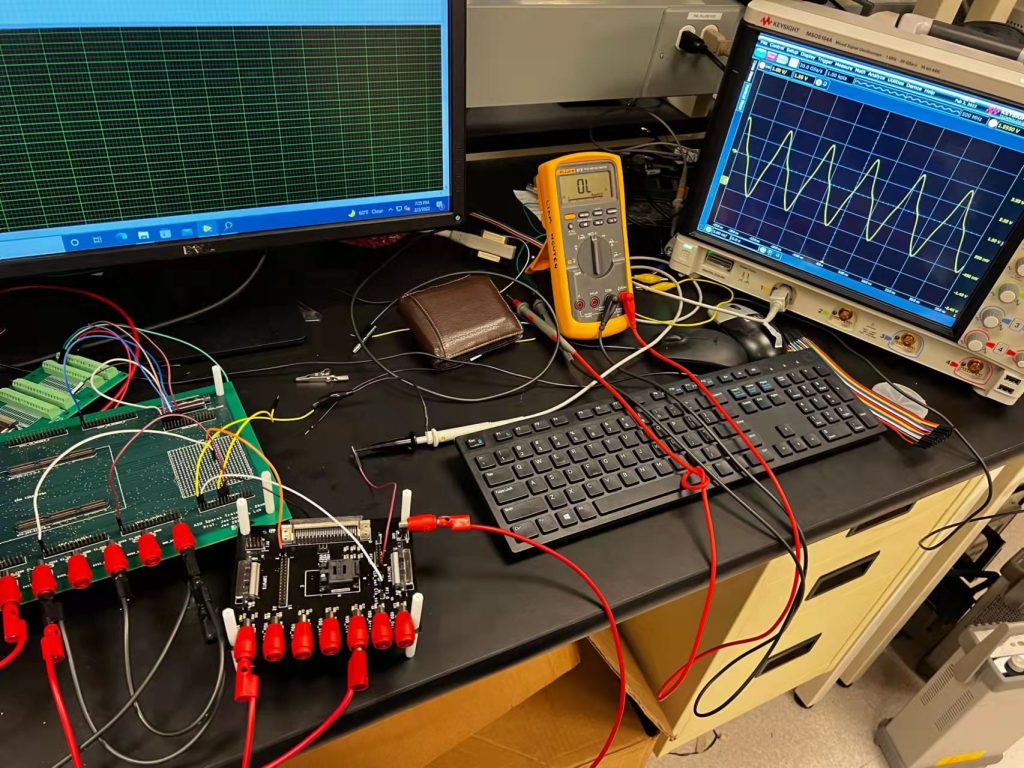

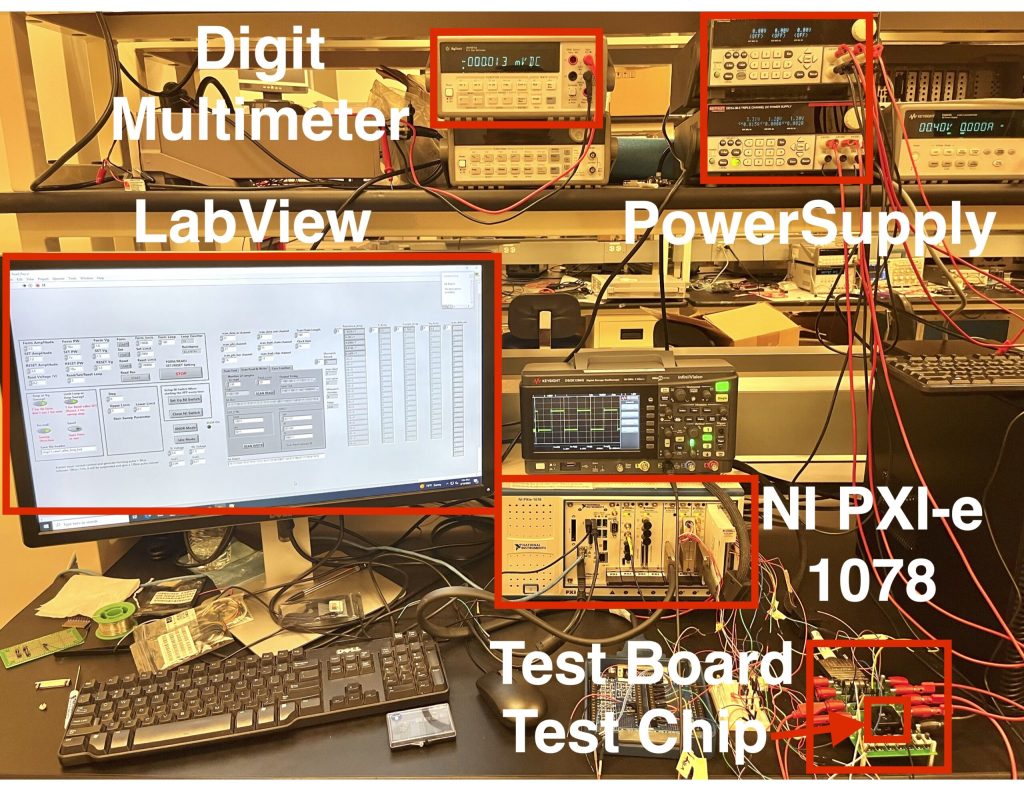

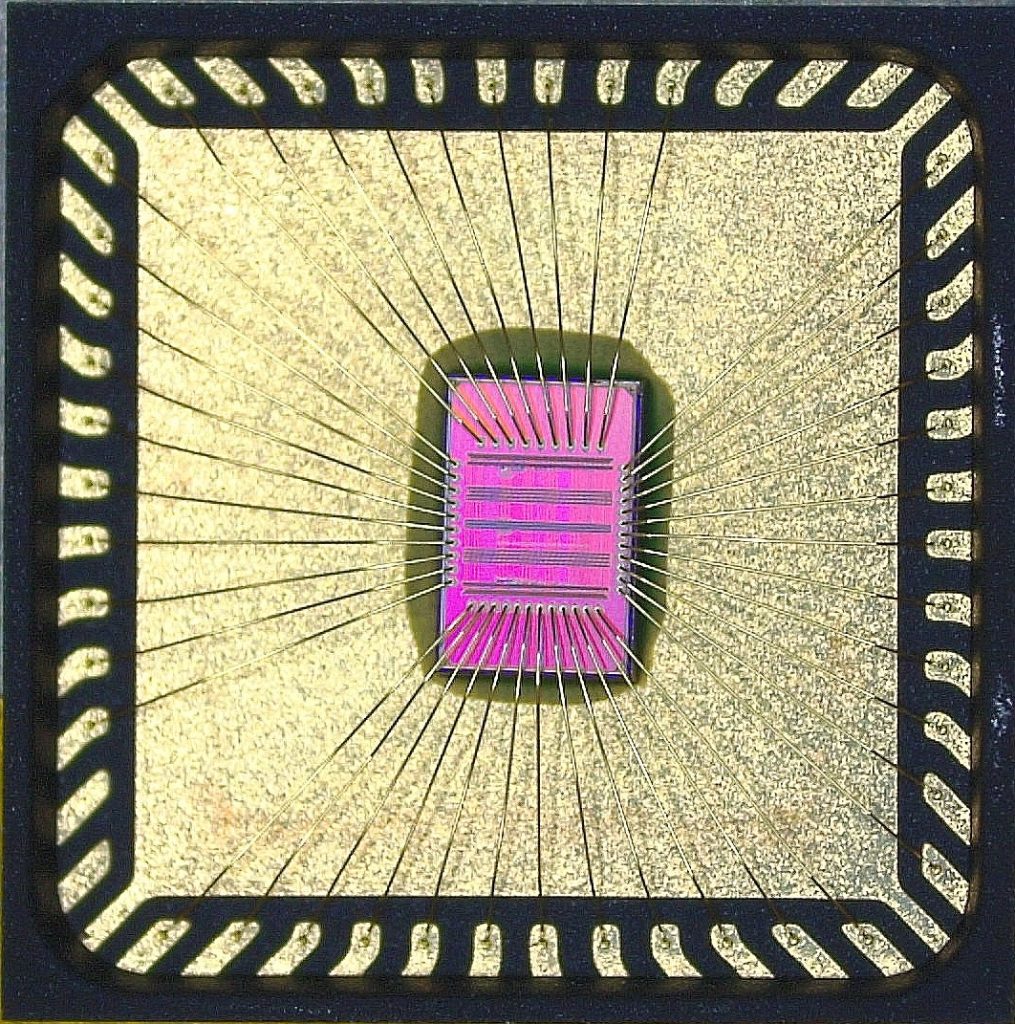

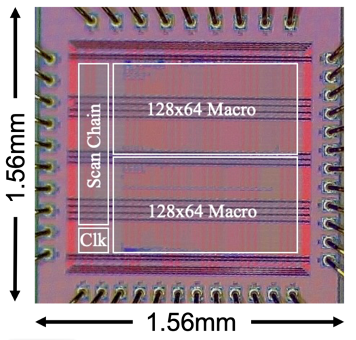

In-memory computing chip prototype samples

Amitesh Sridharan*, Shaahin Angizi*, Sai Kiran Cherupally, Fan Zhang, Jae-sun Seo, and Deliang Fan, “A 1.23-GHz 16-Kb Programmable and Generic Processing-in-SRAM Accelerator in 65nm,” 48th European Solid-State Circuits Conference (ESSCIRC), Milan, Italy, Sep. 19-22, 2022 (* The first two authors contribute equally) [pdf]

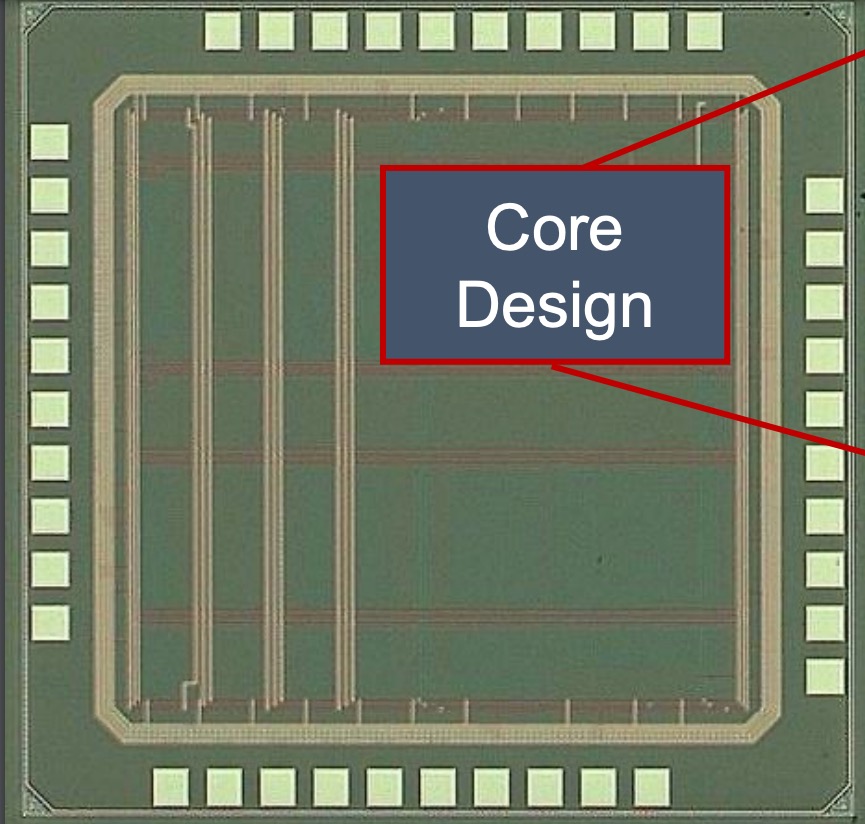

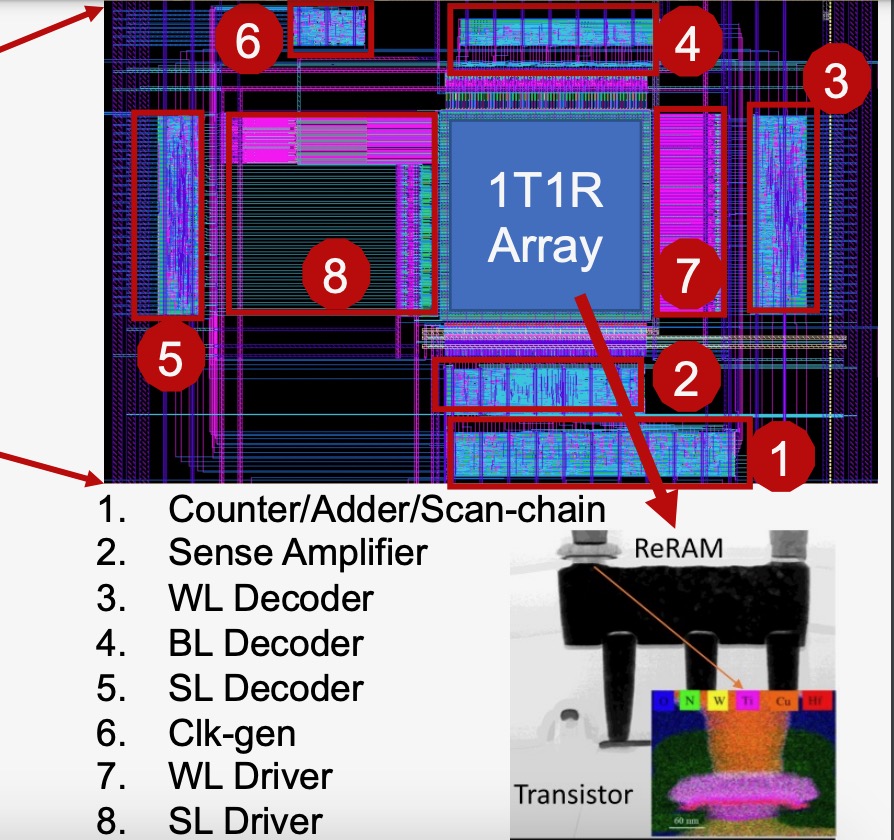

1. Fan Zhang, Wangxin He, Injune Yeo, Maximilian Liehr, Nathaniel Cady, Yu Cao, Jae-sun Seo, and Deliang Fan, “A 65nm RRAM Compute-in-Memory Macro for Genome Sequencing Alignment,” 49th European Solid-State Circuits Conference (ESSCIRC), Lisbon, Portugal, Sep. 11-14, 2023 [pdf]

2. Fan Zhang, Amitesh Sridharan, Wangxin He, Injune Yeo, Maximilian Liehr, Wei Zhang, Nathaniel Cady, Yu Cao, Jae-sun Seo, Deliang Fan “A 65nm RRAM Compute-in-Memory Macro for Genome Processing,” IEEE Journal of Solid State Circuits (JSSC), 2024.

Amitesh Sridharan, Jyotishman Saikia, Fan Zhang, Jae-sun Seo, and Deliang Fan “PS-IMC: A 2385.7 TOPS/W/b Precision Scalable In-Memory Computing Macro with Bit-Parallel Inputs and Decomposable Weights for DNNs,” IEEE Solid-State Circuits Letters (SSCL), 2024 [pdf]

28 nm SRAM based Sparse In-Memory Computing chip design. research paper is published in CICC’24

Amitesh Sridharan, Fan Zhang, Jae-sun Seo, Deliang Fan, “SP-IMC: A Sparsity Aware In-Memory-Computing Macro in 28nm CMOS with Configurable Sparse Representation for Highly Sparse DNN Workloads,” IEEE Custom Integrated Circuits Conference (CICC), 21 – 24 April 2024, Denver, CO.

Related Journal Publications

- [JSSC’24] Fan Zhang, Amitesh Sridharan, Wangxin He, Injune Yeo, Maximilian Liehr, Wei Zhang, Nathaniel Cady, Yu Cao, Jae-sun Seo, Deliang Fan “A 65nm RRAM Compute-in-Memory Macro for Genome Processing,” IEEE Journal of Solid State Circuits (JSSC), 2024.

- [SSCL’24] Amitesh Sridharan, Jyotishman Saikia, Fan Zhang, Jae-sun Seo, and Deliang Fan “PS-IMC: A 2385.7 TOPS/W/b Precision Scalable In-Memory Computing Macro with Bit-Parallel Inputs and Decomposable Weights for DNNs,” IEEE Solid-State Circuits Letters (SSCL), 2024 [pdf]

- [TCAD’24] Fan Zhang, Amitesh Sridharan, William Hwang, Fen Xue, Wilman Tsai, Shan Xiang Wang, and Deliang Fan “On-Device Continual Learning with STT-Assisted-SOT MRAM based In-Memory Computing,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 2024 (accept)

- [JLPEA’24] Shaahin Angizi, Naima Ahmed Fahmi, Deniz Najafi, Wei Zhang, and Deliang Fan “PANDA: Processing in Magnetic Random-Access Memory- Accelerated de Bruijn Graph-Based DNA Assembly,” Journal of Low Power Electronics and Applications. 2024; 14(1):9. https://doi.org/10.3390/jlpea14010009 [pdf]

- [JETCAS’23] Fan Zhang, Shaahin Angizi, Jiao Sun, Wei Zhang, and Deliang Fan “Aligner-D: Leveraging in-DRAM Computing to Accelerate DNA Short Read Alignment,” IEEE Journal on Emerging and Selected Topics in Circuits and Systems, Volume: 13, Issue: 1, March 2023, DOI: 10.1109/JETCAS.2023.3241545[pdf]

- [TMAG’22] William Hwang, Fen Xue, Fan Zhang, Mingyuan Song, Chien-Min Lee, Emrah Turgut, T. C. Chen, Xinyu Bao, Wilman Tsai, Deliang Fan, Shan X. Wang, “Energy Efficient Computing with High-Density, Field-Free STT-Assisted SOT-MRAM (SAS-MRAM),” IEEE Transactions on Magnetics (TMAG) , 2022, DOI: 10.1109/TMAG.2022.3224729 [pdf]

- [Front.Electron.’22] Fan Zhang, Li Yang, Jian Meng, Jae-Sun Seo, Yu Cao and Deliang Fan, “XMA2: A Crossbar-aware Multi-task Adaption Framework via 2-Tier Masks,” Frontier in Electronics, Volume 3 – 2022 | https://doi.org/10.3389/felec.2022.1032485 [pdf]

- [TC’22] Gokul Krishnan, Li Yang, Jingbo Sun, Jubin Hazra, Xiaocong Du, Maximilian Liehr, Zheng Li, Karsten beckmann, Rajiv V. Joshi, Nathaniel C. Cady, Deliang Fan and Yu Cao, “Exploring Model Stability of Deep Neural Networks for Reliable RRAM-based In-Memory Acceleration,” IEEE Transactions on Computers (TC), DOI: 10.1109/TC.2022.3174585, 2022 [pdf]

- [IEEE-Micro’21] Jian Meng, Wonbo Shim, Li Yang, Deliang Fan, Shimeng Yu, and Jae-sun Seo, “Temperature-Resilient RRAM-based In-Memory Computing for DNN Inference,” IEEE Micro, 2021 [pdf]

- [SST’21] Sai Kiran Cherupally, Jian Meng, Adnan Rakin, Shihui Yin, Injue Yeo, Shimeng Yu, Deliang Fan, and Jae-sun Seo, “Improving the Accuracy and Robustness of RRAM-based In-Memory Computing Against RRAM Hardware Noise and Adversarial Attacks,” Semiconductor Science and Technology , 2021 [pdf]

- [IEEE-DT’21] Sai Kiran Cherupally, Jian Meng, Adnan Rakin, Shihui Yin, Mingoo Seok, Deliang Fan and Jae-sun Seo, “Improving DNN Hardware Accuracy by In-Memory Computing Noise Injection,” IEEE Design & Test of Computers , 2021 [pdf]

- [TODAES’21] Shaahin Angizi, Navid Khoshavi, Andrew Marshall, Peter Dowben, and Deliang Fan, “MeF-RAM: A New Non-Volatile Cache Memory Based on Magneto-Electric FET,” ACM Transactions on Automation of Electronic Systems (TODAES) , Volume 27, Issue 2, March 2022, https://doi.org/10.1145/3484222 [pdf]

- [TCAS-II’21] Jian Meng, Li Yang, Xiaochen Peng, Shimeng Yu, Deliang Fan and Jae-Sun Seo, “Structured Pruning of RRAM Crossbars for Efficient In-Memory Computing Acceleration of Deep Neural Networks,” IEEE Transactions on Circuits and Systems- II (TCAS-II) Vol. 68, No. 5, May 2021 [pdf]

- [TMAG’20] Shaahin Angizi, Zhezhi He, An Chen and Deliang Fan, “Hybrid Spin-CMOS Polymorphic Logic Gate with Application in In-Memory Computing,” IEEE Transactions on Magnetics (TMAG) , Volume: 56 , Issue: 2 , Feb. 2020, DOI: 10.1109/TMAG.2019.2955626 [pdf]

- [JETC’20] Zhezhi He, Li Yang, Shaahin Angizi, Adnan Siraj Rakin and Deliang Fan, “Sparse BD-Net: A Multiplication-Less DNN with Sparse Binarized Depth-wise Separable Convolution,” ACM Journal on Emerging Technologies in Computing Systems (JETC), January 2020 Article No.: 15 https://doi.org/10.1145/3369391 [pdf]

- [TCAD’19] Shaahin Angizi, Zhezhi He, Amro Awad and Deliang Fan, “MRIMA: An MRAM-based In-Memory Accelerator,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 27 March 2019, DOI: 10.1109/TCAD.2019.2907886 [pdf]

- [JETC’18] Farhana Parveen, Shaahin Angizi and Deliang Fan, “IMFlexCom: Energy Efficient In-memory Flexible Computing using Dual-mode SOT-MRAM,” ACM Journal on Emgerging Technologies in Computing Systems, Vol.14, no.3, Oct. 2018 [pdf]

- [TMSCS’18] Zhezhi He, Yang Zhang, Shaahin Angizi, Boqing Gong and Deliang Fan, “Exploring A SOT-MRAM based In-Memory Computing for Data Processing,” IEEE Transactions on Multi-Scale Computing Systems, 2018 [pdf]

- [TMAG’18] Farhana Parveen, Shaahin Angizi, Zhezhi He and Deliang Fan, “IMCS2: Novel Device-to-Architecture Co-design for Low Power In-memory Computing Platform using Coterminous Spin-Switch,” IEEE Transactions on Magnetics, vol. 54, no.7, July 2018 [pdf]

- [TCAD’17] S. Angizi, Z. He, N. Bagherzadeh and D. Fan, “Design and Evaluation of a Spintronic In-Memory Processing Platform for Non-Volatile Data Encryption,” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol.37, no.9, Sept. 2018 [pdf]

- Shaahin Angizi, Deliang Fan, “Accelerating Bulk Bit-Wise X(N)OR Operation in Processing-in-DRAM Platform” arXiv:1904.05782, April 2019

Related Conference Publications

- [CICC’24] Amitesh Sridharan, Fan Zhang, Jae-sun Seo, Deliang Fan, “SP-IMC: A Sparsity Aware In-Memory-Computing Macro in 28nm CMOS with Configurable Sparse Representation for Highly Sparse DNN Workloads,” IEEE Custom Integrated Circuits Conference (CICC), 21 – 24 April 2024, Denver, CO.

- [ESSCIRC’23] Fan Zhang, Wangxin He, Injune Yeo, Maximilian Liehr, Nathaniel Cady, Yu Cao, Jae-sun Seo, and Deliang Fan, “A 65nm RRAM Compute-in-Memory Macro for Genome Sequencing Alignment,” 49th European Solid-State Circuits Conference (ESSCIRC), Lisbon, Portugal, Sep. 11-14, 2023 [pdf]

- [ESSCIRC’22] Amitesh Sridharan*, Shaahin Angizi*, Sai Kiran Cherupally, Fan Zhang, Jae-sun Seo, and Deliang Fan, “A 1.23-GHz 16-Kb Programmable and Generic Processing-in-SRAM Accelerator in 65nm,” 48th European Solid-State Circuits Conference (ESSCIRC), Milan, Italy, Sep. 19-22, 2022 (* The first two authors contribute equally) [pdf]

- [ESSCIRC’23] Jyotishman Saikia, Amitesh Sridharan, Injune Yeo, Shreyas Venkataramanaiah, Deliang Fan, Jae-sun Seo, “FP-IMC: a 28nm All-Digital Configurable Floating-Point In-Memory Computing Macro,” 49th European Solid-State Circuits Conference (ESSCIRC), Lisbon, Portugal, Sep. 11-14, 2023 [pdf]

- [DAC’24] Fan Zhang, Amitesh Sridharan, Wilman tsai, Yiran Chen, Shan X. Wang and Deliang Fan, “Efficient Memory Integration: MRAM-SRAM Hybrid Accelerator for Sparse On-Device Learning” In: 61st Design Automation Conference (DAC), San Francisco, CA, June 23-27, 2024 (accept)

- [DAC’24] Fan Zhang, Li Yang and Deliang Fan, “Hyb-Learn: A Framework for On-Device Self-Supervised Continual Learning with Hybrid RRAM/SRAM Memory” In: 61st Design Automation Conference (DAC), San Francisco, CA, June 23-27, 2024 (accept)

- [DAC’24] Qilin Zheng, Ziru Li, Jonathan Ku, Yitu Wang, Brady Taylor, Deliang Fan and Yiran Chen, “Improving the Efficiency of In-Memory-Computing Macro with a Hybrid Analog-Digital Computing Mode for Lossless Neural Network Inference” In: 61st Design Automation Conference (DAC), San Francisco, CA, June 23-27, 2024 (accept)

- [DAC’23] Amitesh Sridharan, Fan Zhang, Yang Sui, Bo Yuan and Deliang Fan, “DSPIMM: Digital Sparse In-Memory matrix vector multplier for Communication Applications” In: 59th Design Automation Conference (DAC), San Francisco, CA, July 9-13, 2023 (accept)

- [DAC’22] Fan Zhang, Li Yang, Jian Meng, Jae-sun Seo, Yu Cao, and Deliang Fan, “XMA: A Crossbar-aware Multi-task Adaption Framework via Shift-based Mask Learning Method” In: 59th Design Automation Conference (DAC), San Francisco, CA, July 10-14, 2022 (accept)

- [DATE’22] Fan Zhang, Li Yang, Jian Meng, Yu Cao, Jae-sun Seo, and Deliang Fan, “XST: A Crossbar Column-wise Sparse Training for Efficient Continual Learning,” Design, Automation and Test in Europe (DATE), 14 – 23 March 2022 ( –Best IP (Interactive Presentations) Paper Award Candidate–)

- [ASPDAC’22] Fan Zhang, Li Yang, Jian Meng, Yu Cao, Jae-sun Seo, and Deliang Fan, “XBM: A Crossbar Column-wise Binary Mask Learning Method for Efficient Multiple Task Adaption,” 27th Asia and South Pacific Design Automation Conference (ASPDAC), Jan. 17-20, 2022 [pdf]

- [DAC’21] Fan Zhang, Shaahin Angizi and Deliang Fan, “Max-PIM: Fast and Efficient Max/Min Searching in DRAM” In: 58th Design Automation Conference (DAC), San Francisco, CA, July 11-15, 2021 [pdf] ( –Best Paper Candidate Nomination–)

- [DAC’21] Fan Zhang, Shaahin Angizi, Naima Ahmed Fahmi, Wei Zhang and Deliang Fan, “PIM-Quantifier: A Processing-in-Memory Platform for Genome Quantification”. In: 58th Design Automation Conference (DAC), San Francisco, CA, July 11-15, 2021 [pdf]

- [SOCC’20] Li Yang, Zhezhi He, Shaahin Angizi and Deliang Fan, “Processing-In-Memory Accelerator for Dynamic Neural Network with Run-Time Tuning of Accuracy, Power and Latency,” 33rd IEEE International System-on-Chip Conference (SOCC), September 8-11, 2020 (invited) [pdf]

- [GLSVLSI’20] Shaahin Angizi, Wei Zhang and Deliang Fan, “Exploring DNA Alignment-in-Memory Leveraging EmergingSOT-MRAM”, 30th edition of the ACM Great Lakes Symposium on VLSI (GLSVLSI), September 7-9, 2020 (invited) [pdf]

- [DAC’20] Shaahin Angizi, Naima Ahmed Fahmi, Wei Zhang and Deliang Fan, “PIM-Assembler: A Processing-in-Memory Platform for Genome Assembly” In: 57th Design Automation Conference (DAC), San Francisco, CA, July 19-23, 2020 [pdf]

- [DATE’20] Shaahin Angizi, Jiao Sun, Wei Zhang and Deliang Fan, “PIM-Aligner: A Processing-in-MRAM Platform for Biological Sequence Alignment,” Design, Automation and Test in Europe (DATE), 09-13 March 2020, ALPEXPO, Grenoble, France [pdf]

- [ASPDAC’20] Li Yang, Shaahin Angizi, Deliang Fan, “A Flexible Processing-in-Memory Accelerator for Dynamic Channel-Adaptive Deep Neural Networks,” Asia and South Pacific Design Automation Conference (ASP-DAC), Jan. 13-16, 2020, Beijing, China [pdf]

- [ICCAD’19] Shaahin Angizi and Deliang Fan, “ReDRAM: A Reconfigurable Processing-in-DRAM Platform for Accelerating Bulk Bit-Wise Operations,” IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 4-7 November 2019, Westminster, CO [pdf]

- [NANOARCH’19] Shaahin Angizi and Deliang Fan, “Deep Neural Network Acceleration in Non-Volatile Memory: A Digital Approach?,” IEEE/ACM International Symposium on Nanoscale Architectures, 17-19 July 2019, Qingdao, CHINA [pdf]

- [ISVLSI’19] Shaahin Angizi, Zhezhi He, Dayane Reis, Xiaobo Sharon Hu, Wilman Tsai, Shy Jay Lin and Deliang Fan, “Accelerating Deep Neural Networks in Processing-in-Memory Platforms: Analog or Digital Approach?,” IEEE Computer Society Annual Symposium on VLSI, 15 – 17 July 2019, Miami, Florida, USA (invited) [pdf]

- [GLSVLSI’19] Shaahin Angizi and Deliang Fan, “GraphiDe: A Graph Processing Accelerator leveraging In-DRAM-Computing,” ACM Great Lakes Symposium on VLSI(GLSVLSI), May 9-11, 2019, Washington, D.C. USA ( Best Paper Award) [pdf]

- [DAC’19] Shaahin Angizi, Jiao Sun, Wei Zhang and Deliang Fan, “AlignS: A Processing-In-Memory Accelerator for DNA Short Read Alignment Leveraging SOT-MRAM,” Design Automation Conference (DAC), June 2-6, 2019, Las Vegas, NV, USA [pdf]

- [DAC’19] Zhezhi He, Jie Lin, Rickard Ewetz, Jiann-Shiun Yuan and Deliang Fan, “Noise Injection Adaption: End-to-End ReRAM Crossbar Non-ideal Effect Adaption for Neural Network Mapping,” Design Automation Conference (DAC), June 2-6, 2019, Las Vegas, NV, USA [pdf] [code in GitHub]

- [DATE’19] Shaahin Angizi, Jiao Sun, Wei Zhang and Deliang Fan, “GraphS: A Graph Processing Accelerator Leveraging SOT-MRAM,” Design, Automation and Test in Europe (DATE), March 25-29, 2019, Florence, Italy. [pdf]

- [ASPDAC’19] Shaahin Angizi, Zhezhi He and Deliang Fan, “ParaPIM: A Parallel Processing-in-Memory Accelerator for Binary-Weight Deep Neural Networks,” Asia and South Pacific Design Automation Conference (ASP-DAC), Jan. 21-24, 2019, Tokyo, Japan [pdf]

- [ICCD’18] Adnan Siraj Rakin, Shaahin Angizi, Zhezhi He and Deliang Fan, “PIM-TGAN: A Processing-in-Memory Accelerator for Ternary Generative Adversarial Networks,” IEEE International Conference on Computer Design (ICCD) , Oct. 7-10, 2018, Orlando, FL, USA [pdf]

- [ICCAD’18] Shaahin Angizi, Zhezhi He and Deliang Fan, “DIMA: A Depthwise CNN In-Memory Accelerator,” IEEE/ACM International Conference on Computer Aided Design, Nov. 5-8, 2018, San Diego, CA, USA [pdf]

- [ISVLSI’18] Zhezhi He, Shaahin Angizi, Adnan Siraj Rakin and Deliang Fan, “BD-NET: A Multiplication-less DNN with Binarized Depthwise Separable Convolution,” IEEE Computer Society Annual Symposium on VLSI, July 9-11, 2018, Hong Kong, CHINA [pdf] ( Best Paper Award)

- [ISVLSI’18] Zhezhi He, Shaahin Angizi and Deliang Fan, “Accelerating Low Bit-Width Deep Convolution Neural Network in MRAM,” IEEE Computer Society Annual Symposium on VLSI, July 9-11, 2018, Hong Kong, CHINA (invited) [pdf]

- [DAC’18] Shaahin Angizi*, Zhezhi He*, Adnan Siraj Rakin and Deliang Fan, “CMP-PIM: An Energy-Efficient Comparator-based Processing-In-Memory Neural Network Accelerator,” IEEE/ACM Design Automation Conference (DAC), June 24-28, 2018, San Francisco, CA, USA (* The first two authors contributed equally) [pdf]

- [DAC’18] Shaahin Angizi, Zhezhi He and Deliang Fan, “PIMA-Logic: A Novel Processing-in-Memory Architecture for Highly Flexible and Energy-Efficient Logic Computation, ” IEEE/ACM Design Automation Conference (DAC), June 24-28, 2018, San Francisco, CA, USA [pdf]

- [ASPDAC’18] F. Parveen, Z. He, S. Angizi and D. Fan, “HieIM: Highly Flexible In-Memory Computing using STT MRAM,” Asia and South Pacific Design Automation Conference (ASP-DAC), Jan. 22-25, 2018, Jeju Island, Korea [pdf]

- [ASPDAC’18] S. Angizi, Z. He, F. Parveen and D. Fan, “IMCE: Energy-Efficient Bit-Wise In-Memory Convolution Engine for Deep Neural Network,” Asia and South Pacific Design Automation Conference (ASP-DAC), Jan. 22-25, 2018, Jeju Island, Korea [pdf]

- [ICCD’17] Z. He, S. Angizi and D. Fan, “Exploring STT-MRAM based In-Memory Computing Paradigm with Application of Image Edge Extraction,” IEEE International Conference on Computer Design (ICCD) , Nov. 5-8, 2017, Boston, MA [pdf]

- [ICCD’17] D. Fan and S. Angizi “Energy Efficient In-Memory Binary Deep Neural Network Accelerator with Dual-Mode SOT-MRAM,” IEEE International Conference on Computer Design (ICCD) , Nov. 5-8, 2017, Boston, MA [pdf]

- [NCAMA’17] S. Angizi and D. Fan , “IMC: Energy-Efficient In-Memory Convolver for Accelerating Binarized Deep Neural Network,” Neuromorphic Computing Symposium: Architectures, Models, and Applications , July 17-19, 2017, Knoxville, Tennessee [pdf]

- [ISLPED’17] F. Parveen, S. Angizi, Z. He and D. Fan , “Low Power In-Memory Computing based on Dual-Mode SOT-MRAM,” IEEE/ACM International Symposium on Low Power Electronics and Design, July 24-26, 2017, Taipei, Taiwan [pdf]

- [NANOARCH’17] Z. He, S. Angizi, F. Parveen and D. Fan , “High Performance and Energy-Efficient In-Memory Computing Architecture based on SOT-MRAM,” IEEE/ACM International Symposium on Nanoscale Architectures , July 25-26, 2017, Newport, USA [pdf]

- [ISVLSI’17] D. Fan, S. Angizi and Z. He, “In-Memory Computing with Spintronic Devices,” IEEE Computer Society Annual Symposium on VLSI (ISVLSI), July 3-5, 2017, Bochum, Germany (invited) [pdf]

- [ISVLSI’17]S. Angizi, Z. He, F. Parveen and D. Fan, “RIMPA: A New Reconfigurable Dual-Mode In-Memory Processing Architecture with Spin Hall Effect-Driven Domain Wall Motion Device,” IEEE Computer Society Annual Symposium on VLSI (ISVLSI), July 3-5, 2017, Bochum, Germany [pdf]

- [ISVLSI’17]F. Parveen, Z. He, S. Angizi and D. Fan, “Hybrid Polymorphic Logic Gate with 5-Terminal Magnetic Domain Wall Motion Device,” IEEE Computer Society Annual Symposium on VLSI (ISVLSI), July 3-5, 2017, Bochum, Germany [pdf] ( Best Paper Award)

- [MWSCAS’17]D. Fan, Z. He and S. Angizi, “Leveraging Spintronic Devices for Ultra-Low Power In-Memory Computing: Logic and Neural Network,” 60th IEEE International Midwest Symposium on Circuits and Systems, Aug. 6-9, 2017, Boston, MA, USA (invited) [pdf]

- [ISCAS’17]F. Parveen, S. Angizi, Z. He and D. Fan, “Hybrid Polymorphic Logic Gate Using 6 Terminal Magnetic Domain Wall Motion Device,” IEEE International Symposium on Circuits & Systems (ISCAS), Baltimore, MD, USA, May 28-31, 2017 [pdf]

- [GLSVLSI’17]Z. He, S. Angizi, F. Parveen, and D. Fan, “Leveraging Dual-Mode Magnetic Crossbar for Ultra-low Energy In-Memory Data Encryption”, 27th GLSVLSI, Banff, Alberta, Canada, May 10-12, 2017 [pdf]

- [GLSVLSI’17]S. Angizi, Z. He, and D. Fan, “Energy Efficient In-Memory Computing Platform Based on 4-Terminal Spin Hall Effect-Driven Domain Wall Motion Devices”, 27th GLSVLSI, Banff, Alberta, Canada, May 10-12, 2017 [pdf]

- [NANOARCH’16]D. Fan, “Low Power In-Memory Computing Platform with Four Terminal Magnetic Domain Wall Motion Devices”, IEEE/ ACM International Symposium on Nanoscale Architectures, , Beijing, China, July 18-20, 2016 [pdf]