# The Digital Abstraction

Andreas G. Andreou

# logic levels definitions

| Logical value | Voltage                | Name | Symbol in DSCH                          | Symbol in Microwind                  |

|---------------|------------------------|------|-----------------------------------------|--------------------------------------|

| 0             | 0.0V                   | VSS  | 77777<br>(Green in logic<br>simulation) | f<br>(Green in analog<br>simulation) |

| 1             | 1.2V in emos<br>0.12μm | VDD  | (Red in logic<br>simulation)            | (Red in analog simulation)           |

| Х             | Undefined              | Х    | (Gray in simulation)                    | (Gray in simulation)                 |

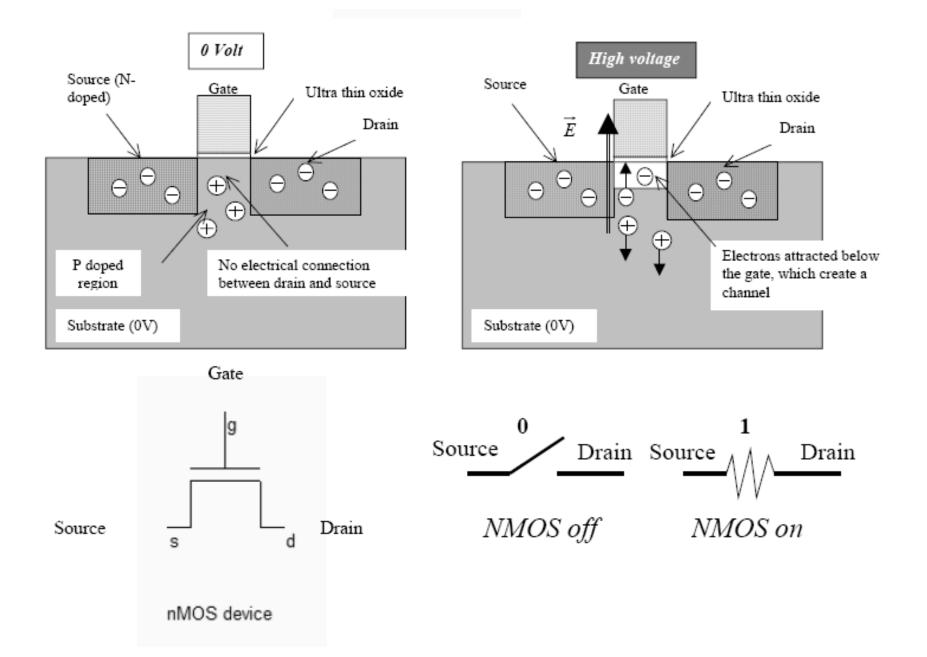

# **MOS transistor**

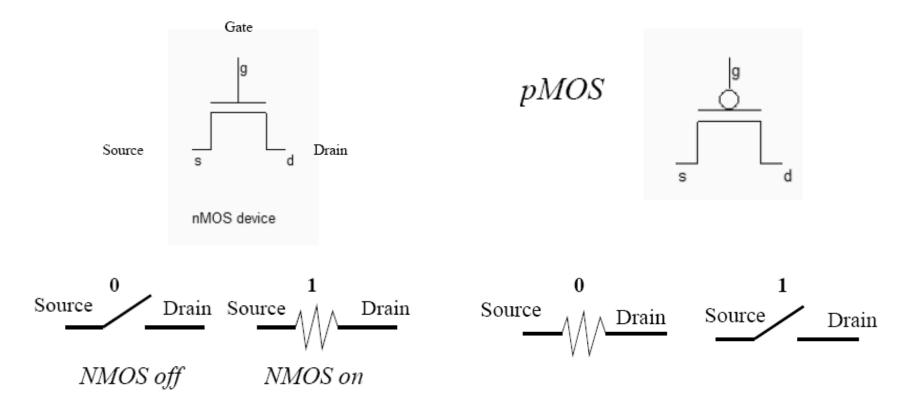

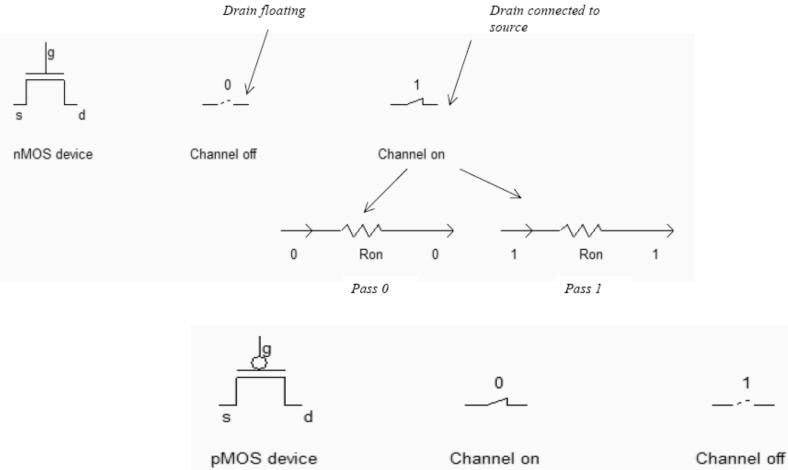

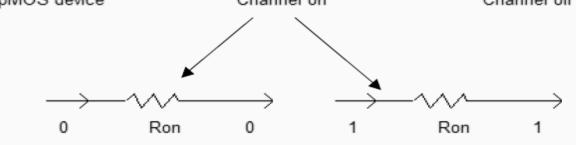

# NMOS and PMOS digital "models"

| Gate | Source | Drain |

|------|--------|-------|

| 0    | 0      | Х     |

| 0    | 1      | Х     |

| 1    | 0      | 0     |

| 1    | 1      | 1     |

| Gate | Source | Drain |

|------|--------|-------|

| 0    | 0      | 0     |

| 0    | 1      | 1     |

| 1    | 0      | Х     |

| 1    | 1      | Х     |

# what does this all mean?

1

### and back to layout

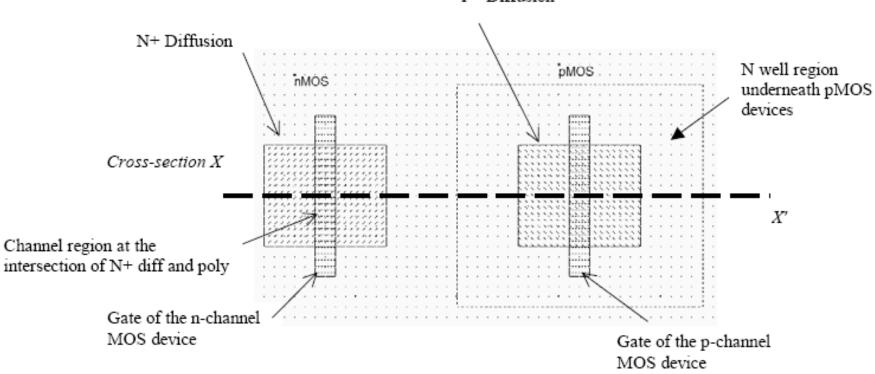

P+ Diffusion

Figure 2-14: Bird's view of the n-channel and p-channel MOS device layout (allMosDevices.MSK)

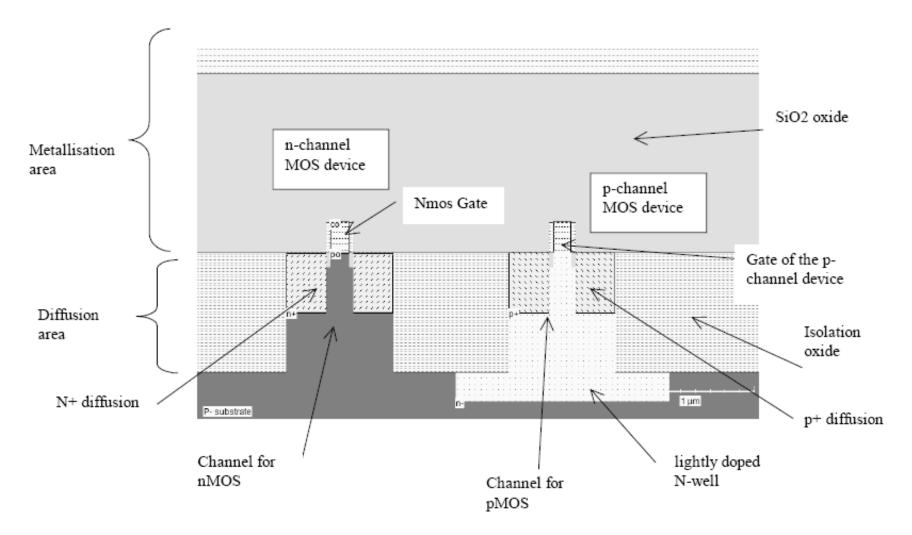

#### cross-section and zoom

Figure 2-15: Vertical cross-section of an n-channel and p-channel MOS devices in 0.12µm technology

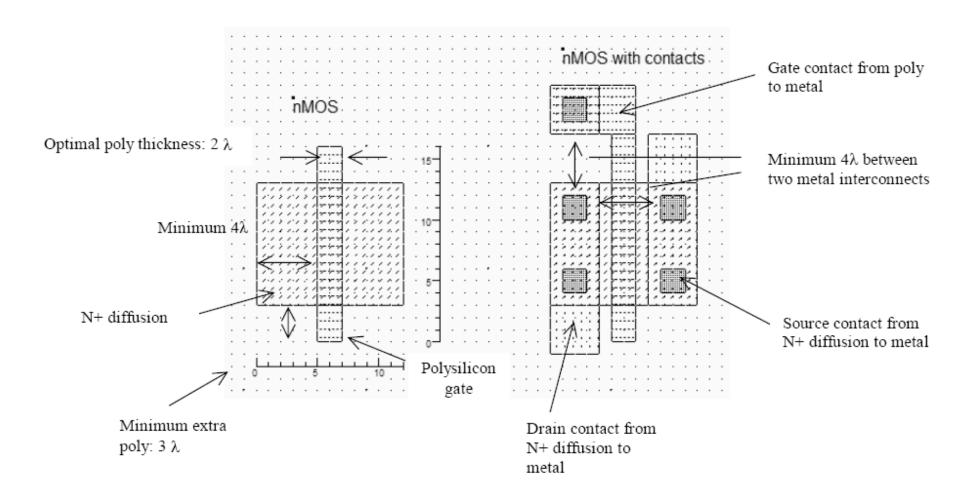

# **MOS transistor layout**

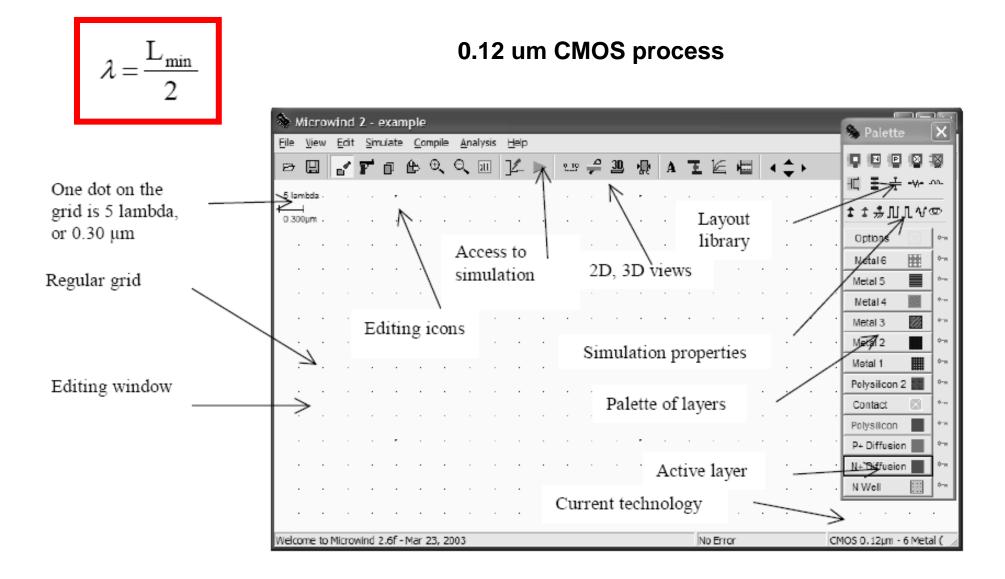

# microwind

#### more notation

| Layer name           | Code    | Description                                                                                                                                                          | Color in Microwind |

|----------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Polysilicon          | Poly    | Gate of the n-channel and p-channel MOS devices                                                                                                                      | Red                |

| N+ diffusion         | Diffn   | Delimits the active part of the n-channel device. Also used<br>to polarize the N-well                                                                                | Dark green         |

| P+ diffusion         | Diffn   | Delimits the active part of the p-channel device. Also used<br>to polarize the bulk                                                                                  | Maroon             |

| Contact              | Contact | Makes the connection between diffusions and metal for<br>routing. The contact plug is fabricated by drilling a hole in<br>the oxide and filling the hole with metal. |                    |

| First level of metal | Metal1  | Used to rout devices together, in order to create the logic<br>or analog function                                                                                    | Blue               |

| N well               | Nwell   | Low doped diffusion used to invert the doping of the<br>substrate. All p-channel MOS are located within N well<br>areas.                                             | c                  |

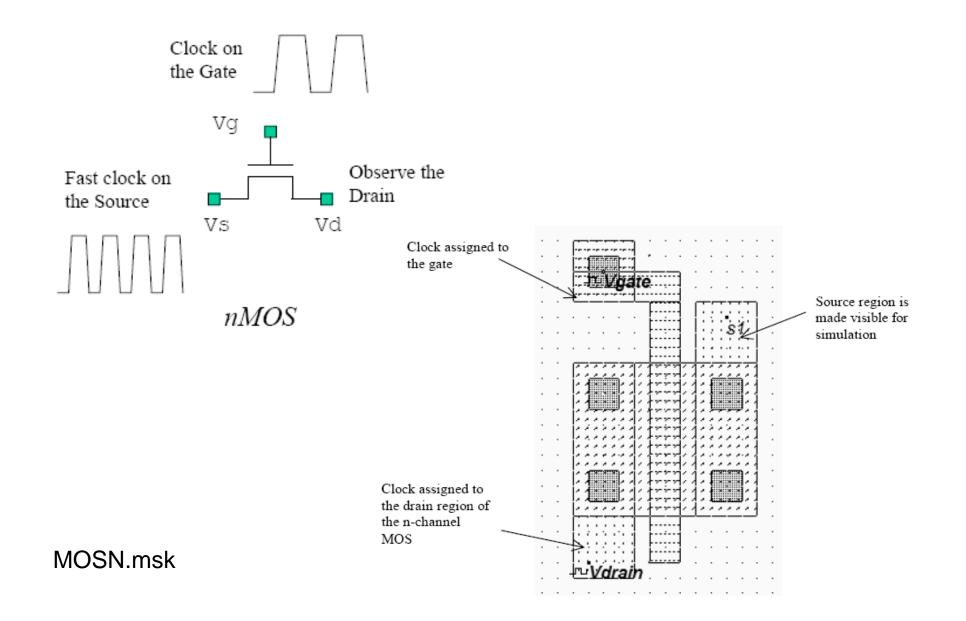

#### dynamic behavior: another level of abstraction

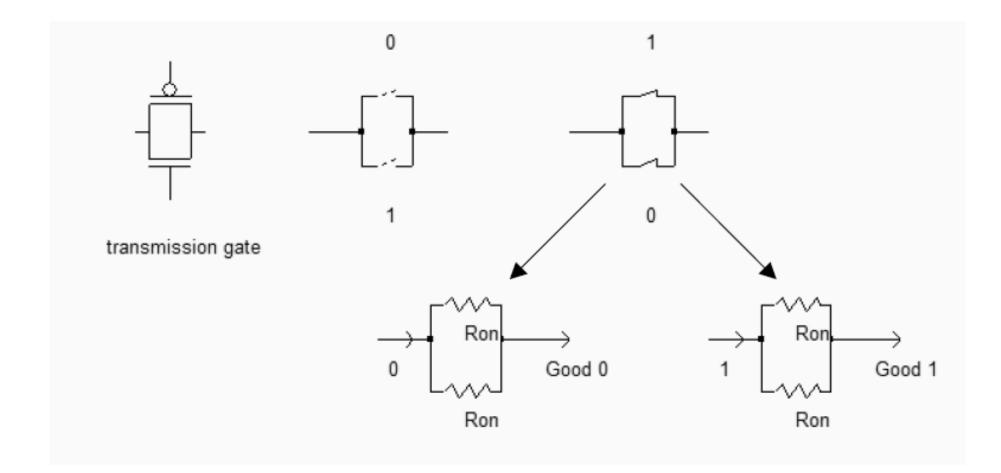

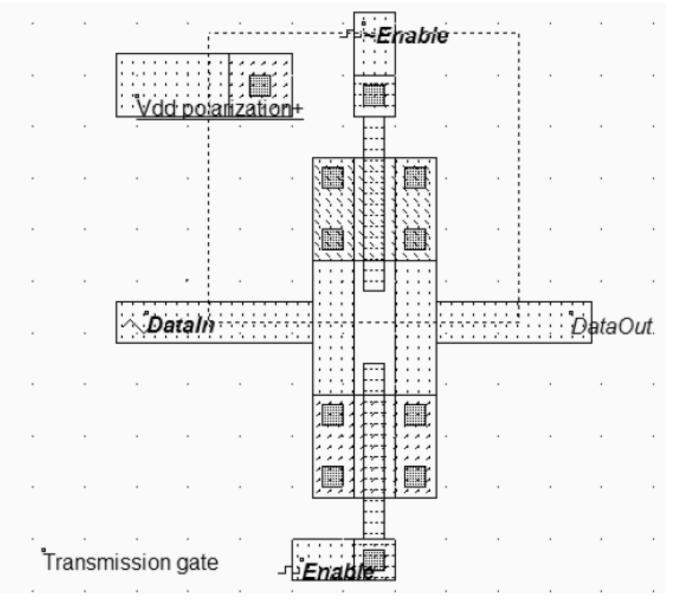

### and the perfect switch!

### simulation of the perfect switch

TGATE.msk

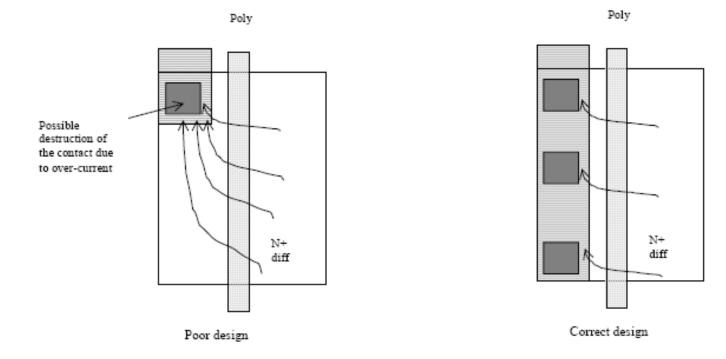

### multiple contacts: why?

Fig.2-46. A strong current through a single contact could damage the metal structure.

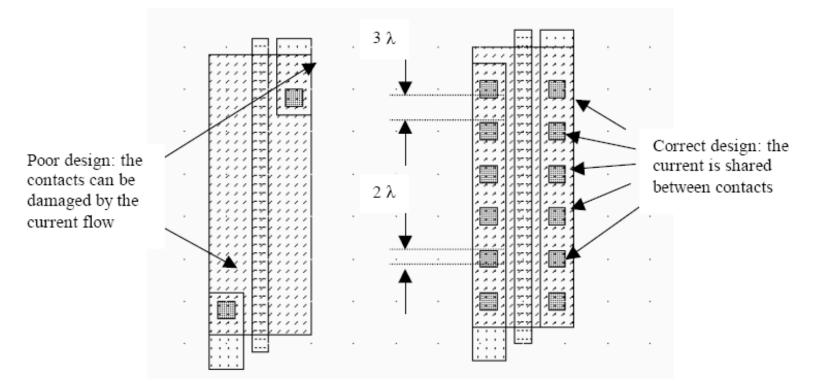

# multiple contacts

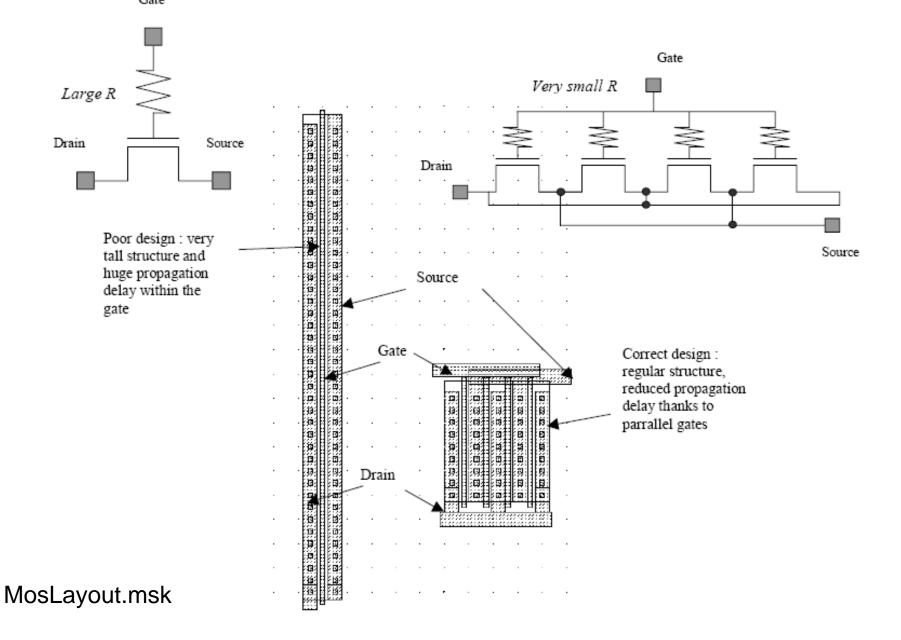

Fig.2-47. A single contact cannot handle more that 1mA. A series of contacts is preferred (MosLayout.MSK)

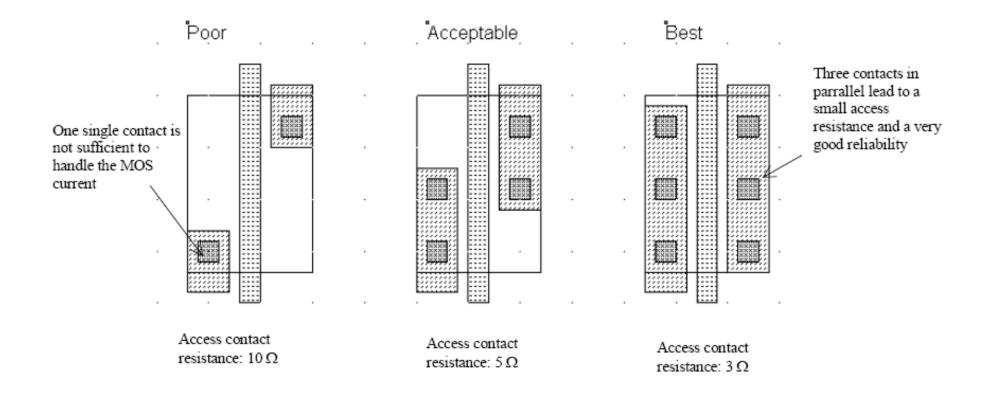

### multiple contacts

Fig.2-48. A series of contacts also reduced the serial access resistance(MosContacts.MSK)

# multiple gates